发布时间:2025-08-08编辑:国产MOS管厂家浏览:0次

在集成电路设计领域,工程师们常常面临一个经典难题:如何在有限空间内实现高压耐受能力?传统方案多依赖昂贵的专用高压器件,而一项创新技术正悄然改变这一局面——通过低压MOS管堆叠结构实现耐高压性能。这种设计不仅突破物理限制,更在能效与成本间找到精妙平衡点。

低压堆叠的科学原理

当底层Nmos处于关断状态时,上方M2管的源极电压稳定在VDD/2区间,其栅极则维持VDD/2-VD的特殊电位差。这种精密的电压分配机制如同天平两端的砝码,确保每个晶体管都处在安全工作区。特别值得注意的是电容储能效应:当M1导通瞬间,M2栅极电荷被存储于寄生电容中,形成类似水坝缓释水流的效果,使电压变化趋于平缓。双重保险机制下,无论是静态关断还是动态切换,所有器件均能避免雪崩击穿风险。

与传统方案的效能对比

相较于单个高压LDMOS结构,多级低压管串联展现出显著优势。以电源管理芯片为例,输入电压仅5V的场景原本只需普通低压器件即可胜任,但采用堆叠设计后却获得意外收益:器件面积缩减如同将三层蛋糕压缩成双层慕斯,同时能耗降低犹如替换了更高效的节能灯泡。更关键的是无需额外电源轨支持,彻底摆脱了复杂供电网络的束缚。

工程实现的智慧突破

实际布局中,设计师们运用梯度掺杂工艺改造N型漂移区为低浓度P型区域,这恰似加固河堤时的分层夯实法,逐层提升材料的绝缘强度。针对低频信号传输痛点,新型结构在源漏间并联阻抗元件,相当于给电流开辟专用通道,有效增强弱信号承载能力。这些微创新如同精密钟表的内部齿轮,共同驱动整个系统的高效运转。

应用场景的革命性拓展

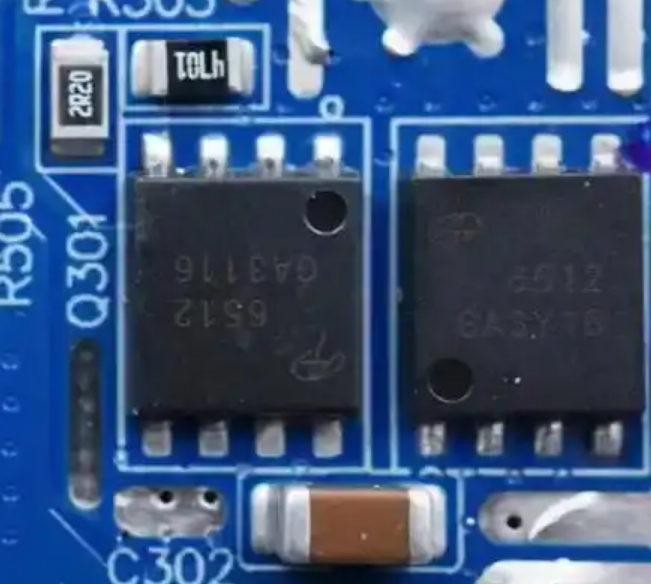

该技术已渗透到多个前沿领域:在快充适配器中,它让娇小的PCB板承载百倍于自身的电压冲击;于电机驱动器里,密集排列的低压管阵列取代粗犷的高压模块,实现动力系统的瘦身革命。就像用乐高积木搭建摩天大楼,看似脆弱的基础单元通过结构化组合迸发出惊人力量。

未来演进的技术图谱

随着半导体工艺持续微缩,三维堆叠成为必然趋势。研究者正在探索向N极方向扩展的可能性,如同将二维画作升级为立体雕塑。结合先进封装技术的异质集成方案,有望催生出兼具高性能与高性价比的新型功率器件家族。这种自上而下的创新路径,正在重塑电力电子领域的生态格局。

这项源于基础物理规律的技术革新,本质上是对摩尔定律精神的延续——通过聪明的系统架构设计,而非单纯依赖材料突破,持续推动集成电路性能边界。当工程师们跳出单一器件的思维定式,转而用系统级视角审视问题时,那些曾经被视为不可逾越的技术壁垒,正在变成通向新世界的旋转门。

上一篇:MOS管组成的无极性电路设计

下一篇:mos管高端驱动电路

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN