发布时间:2025-06-20编辑:国产MOS管厂家浏览:0次

当单个mosfet无法满足系统的大电流需求时,将多个器件并联使用,无疑是工程师们提升功率处理能力的直接思路。**MOS管当然可以并联**,这不仅在理论层面成立,更是大功率应用场景中的常见技术方案。然而,并联并非简单地将引脚连接在一起就能成功。**深入理解其潜在挑战并实施精准的设计策略,是实现高效、可靠分布式电流承载的关键所在。**

**一、mosFET并联的价值与优势**

驱动大功率负载(如电机、电源转换器、逆变器)时,单个MOSFET可能受限于其最大额定电流(如公式:*P_loss = I² * Rds(on)*所示)或散热能力。并联使用多个器件带来了显著优势:

1. **有效提升载流能力:** 并联MOSFET的总导通电阻(Req)理论上小于单个器件的导通电阻,允许更大的总电流通过(公式:*1/Req ≈ 1/Rds(on)1 + 1/Rds(on)2 + ...*)。

2. **显著改善散热分布:** 功率损耗能更均匀地分散在多个器件和更大的散热表面积上,有效降低单个管芯的温升,**提升系统的整体热可靠性**。

3. **优化成本效益:** 在特定电流范围内,选用数个成本较低的中等功率MOSFET并联,可能比选用单一超大功率器件更具经济性。

**二、并联MOSFET面临的三大核心挑战与对策**

并联看似简单,实则隐藏着**电流分配不均可能导致器件失效甚至连锁损坏**的风险。主要挑战在于:

1. **静态均流问题(直流或低频)**

* **根源:** 并联MOSFET之间固有参数的差异,特别是**阈值电压(Vgs(th))和导通电阻(Rds(on))的离散性**。即使施加相同的栅源电压(Vgs), Vgs(th) 稍低的器件会率先导通并获得更多电流;同时, Rds(on) 更小的器件在导通状态下也会自然吸引更多电流(公式:*I ∝ 1/Rds(on)*)。

* **对策:**

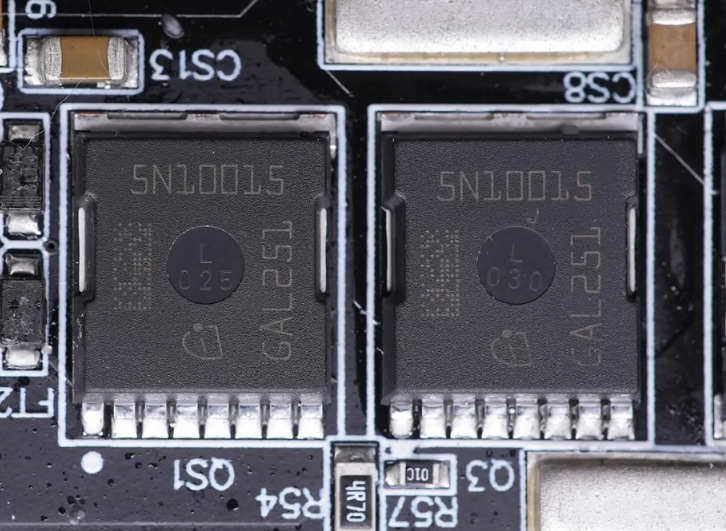

* **精细化匹配选型:** 尽量选择**同一生产批次**的MOSFET,其参数离散性相对较小。在要求严苛的应用中,可对 Vgs(th) 和 Rds(on) 进行严格筛选配对。

* **源极串联均流电阻:** 在每个MOSFET的源极串联一个小阻值电阻(典型值:毫欧级别)。该电阻引入的负反馈作用能有效抑制电流不平衡:当某管电流增大时,其源极电阻压降增大,等效于降低了该管的 Vgs,从而迫使电流趋向均衡。需仔细计算其阻值,权衡均流效果与带来的额外功耗。

2. **动态均流问题(开关瞬态)**

* **根源:** 开关过程中,并联器件之间**开启速度(Turn-on)和关断速度(Turn-off)的差异**。导致开关瞬间各管承受的电流和电压应力截然不同。

* **成因:**

* **驱动电路差异:** 驱动信号路径长度、栅极电阻(Rg)、PCB寄生电感等的微小不对称。

* **器件参数差异:** 栅极电荷(Qg)、米勒平台电压等的不同。

* **对策:**

* **对称布局是基石:** **驱动电路必须严格对称**。确保到每个MOSFET栅极的走线长度、宽度完全相同,并使用相同的栅极电阻(Rg)。**共用功率回路**(Vbus电容、MOSFET、电源地)的设计同样要求对称以平衡寄生电感。

* **独立栅极驱动:** 为每个MOSFET配置独立的栅极驱动电阻(Rg),这比共享一个电阻更有利于平衡驱动电流和开关速度。

* **加强栅极驱动能力:** 使用足够强劲的驱动芯片,确保能快速为多个并联栅极电容(Ciss)充放电,减少开关时间。

3. **热稳定性与热失控风险**

* **根源:** **Rds(on) 具有正温度系数**——温度升高,Rds(on) 增大。如果因初始不均流或散热差异导致某管温度升高→其 Rds(on) 增大→流经它的电流倾向减小?错!在并联结构中,电流会重新分配到更“凉爽”、Rds(on) 更小的器件上,导致这些器件电流进一步增加、温度进一步升高,陷入恶性循环(**“热失控”或“电流虹吸”效应**)。

* **对策:**

* **强制的热耦合:** **将所有并联的MOSFET安装在同一块大面积、高性能的散热器上**,并确保它们之间以及它们与散热器的热阻尽可能低(使用高质量导热硅脂/垫片并施加合适的安装压力)。目标是使所有管芯温度尽可能一致,消除热正反馈回路的基础。

* **充分的散热余量设计:** 散热器尺寸需留有充分裕量,确保即使在最大负载和最坏工况下,管壳温度(Tc)也远低于安全限值。

* **温度监测保护:** 在高可靠性应用中,考虑在散热器关键点或MOSFET管壳上加装温度传感器(如NTC),实现过热保护。

**三、成功实施并联的关键设计实践**

1. **PCB布局的艺术:** 对称性、缩短高电流路径、减小环路面积是核心原则。功率回路(尤其是源极到功率地的路径)必须对称且低阻抗,避免引入额外的寄生电感导致电压不平衡。栅极驱动走线应等长、屏蔽或远离噪声源。

2. **门极电路优化:** 选择合适阻值的栅极电阻(Rg),在开关速度(效率)和抑制振荡/过冲之间取得平衡。有时在栅极和源极间并联一个小电容(Cgs_ext)有助于抑制开关过程中的寄生振荡。

3. **精心选型匹配:** 优先选择参数一致性好的型号和批次。关注 Rds(on)、Vgs(th)、Qg、封装热阻(Rthjc) 等关键参数。

4. **充分的测试验证:** 在样机阶段,**务必使用电流探头实测每个并联支路的电流波形**,重点关注静态电流分配和动态开关瞬态的电流均衡度。同时严格监测各器件的温升。

**MOSFET的并联应用虽然不是无脑连接,但只要工程师深刻理解其中的物理机制——特别是参数的离散性、开关行为的差异以及温度效应的正反馈风险——并采取上述系统性的设计措施(对称驱动、热耦合、参数匹配、精密布局),就能充分发挥并联带来的巨大功率扩展优势,构建出高效、可靠且具性价比的大功率电子系统。**

上一篇:常用的mos管驱动方式

下一篇:n沟道mos管是增强还是耗尽

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN