发布时间:2025-06-26编辑:国产MOS管厂家浏览:0次

在电子电路中,MOS管(金属氧化物半导体场效应管)的设计与应用一直是工程师关注的焦点。其中,源极与栅极短接的配置虽然看似简单,却隐藏着独特的工作原理与潜在风险。这种设计通过将栅极和源极直接连接,形成一种特殊的电路状态,既可能带来性能优势,也可能引发意料之外的问题。

栅源短接的基本原理

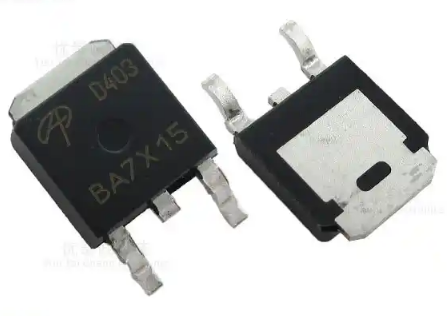

mos管的核心结构包括栅极(G)、源极(S)和漏极(D)三个电极。正常情况下,栅极电压(Vgs)控制源极与漏极之间的电流。当栅极与源极短接时,两者电位差强制归零(Vgs=0),此时管子处于常关状态——即无外部驱动时,漏极电流几乎为零。这种特性常被用于测试场景,例如用万用表检测mos管:短接栅源极后,管子关断;若触碰栅极再恢复,管子会因电荷保持效应而持续导通,直到再次短接栅源极复位。

然而,栅源短接的设计并非仅用于测试。在功率放大器中,这种配置可实现高增益放大。由于栅源短接消除了栅极电压的独立控制,管子工作点完全由漏极电压决定,形成一种自偏置电路,适合高频或高功率应用。

应用场景与性能优势

栅源短接的MOS管在音频、视频和电源领域表现突出。例如,在功率放大器中,其高速度、低噪音的特性可减少信号失真;在开关电路中,快速响应的优势能提升系统效率。这种设计还简化了电路结构,无需额外的偏置电压网络,降低了设计复杂度。

但需注意,短接后的MOS管动态响应受限。由于栅极与源极电位绑定,管子无法灵活响应快速变化的信号,可能影响高频应用的稳定性。

潜在风险与失效机制

若栅源短接为意外故障(如焊接错误或器件损坏),后果可能截然不同。此时,MOS管完全失去控制能力,输出信号无法保障,甚至导致整个电路功能瘫痪。更严重的是,若短接伴随静电放电(ESD),脆弱的栅极氧化层可能击穿,永久损坏器件。

对比来看,栅极与漏极短接的危害更为显著。这种异常会导致Vgs与漏极电压耦合,迫使管子持续工作在饱和区,引发逻辑混乱、振荡甚至过热。

设计中的权衡与解决方案

工程师需根据需求选择是否采用栅源短接。若追求简化设计或特定增益,可主动利用这一配置;但需通过保护电路(如并联稳压二极管)防止ESD损伤。对于高频应用,可改用独立栅极驱动方案,平衡性能与灵活性。

理解MOS管的短接效应,不仅是理论课题,更是实践中的关键技能。从测试方法到系统设计,这种看似简单的连接方式,背后折射出电子器件控制的精妙与复杂。

上一篇:mos管对静电的防护电路

下一篇:mos管关断时的米勒效应

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN