发布时间:2026-04-20编辑:国产MOS管厂家浏览:0次

你有没有遇到过这种情况:同一颗MOS管,数据手册看起来“开关很快”,可一上板子就变得拖泥带水——波形边沿钝、损耗上升、温升也跟着来。

很多时候,问题并不在mos管“本体反应慢”,而在它开关瞬间必须经历的一件事:把与电路相关的杂散电容充电、放电。而在这条“充放电的路”上,栅源极间的等效电容和驱动电路内阻,往往就是决定快慢的两只关键手。

这篇就只盯住一个关系:栅源电容与驱动内阻的相互作用,mos管的开关速度为什么会被它们“卡住”。

先把结论放在前面:MOS管快慢,主要被“充放电时间”决定

参考材料里有个很重要的判断:MOS管在导通与截止两种状态转换时存在过渡过程,但动态特性主要取决于与电路有关的杂散电容充、放电所需的时间;而管子本身导通和截止时电荷积累和消散的时间很小。

这句话的潜台词是:

MOS管不是“想开就开、想关就关”,它先得把相关电容的电荷搬运完,电压才能跟上,电流才会真正改变。

于是“速度”就变成了一个很朴素的电路问题:时间常数。

从一个最直观的动态过程说起:电容怎么把边沿拉长

材料中给了一个NMOS组成电路的动态特性例子,逻辑非常清晰:

当输入电压由高变低,MOS管从导通到截止,电源 UDD 通过 RD 向杂散电容 CL 充电,充电时间常数

τ1 = RD·CL

所以输出电压要延时一段时间才从低变高。

当输入电压由低变高,MOS管从截止到导通,杂散电容 CL 上的电荷通过 rDS 放电,放电时间常数

τ2 ≈ rDS·CL

输出电压也要延时才从高变低。

并且材料特别指出:因为 rDS 比 RD 小得多,所以从截止到导通的转换时间通常比从导通到截止短。

如果你把这件事映射到“栅极驱动”上,思路其实一样:

你给栅极一个电压变化,本质就是在给“栅极相关的等效电容”充放电;而充放电路径的电阻越大,时间常数越大,栅压变化越慢,开关就越慢。

栅源极间电容:它不是“一个数”,而是一段必须完成的“搬运量”

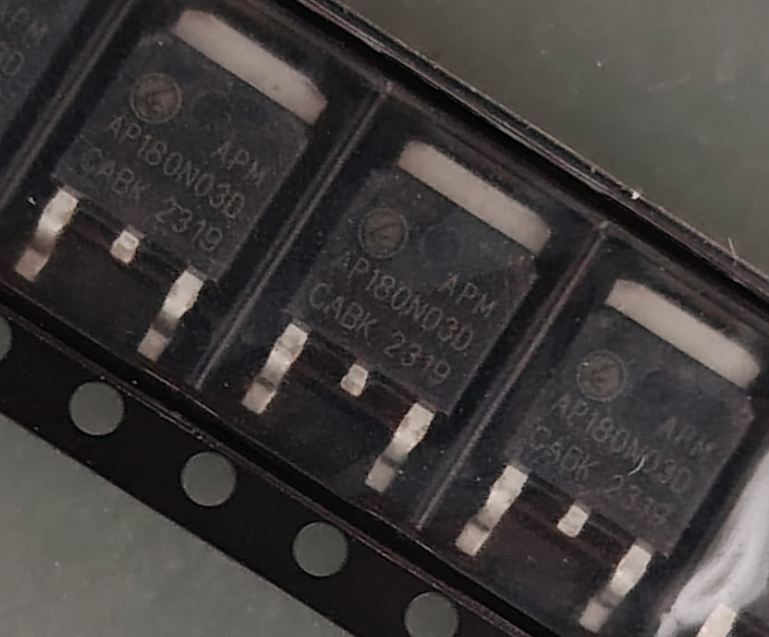

材料后面提到:mosfet 的开关速度和 Cin 充放电有很大关系,使用者无法降低 Cin。

这里的 Cin,你可以把它理解成驱动端“看到”的输入电容(包含栅极相关电容的等效结果)。它带来的影响很直接:

Cin 越大,要把栅极电压推上去或拉下来,就需要搬运更多电荷;

搬运更多电荷,就意味着在相同驱动能力下,需要更长时间。

所以当你觉得“同样的驱动,换了颗MOS就变慢”,往往是因为你换到了一颗等效输入电容更“吃电荷”的器件。

这也是为什么材料说:使用者无法降低 Cin——器件结构决定了它就是要这么多“充放电量”。

驱动内阻:它决定你“搬运电荷”的速度上限

Cin 决定“要搬多少”,那驱动电路内阻(材料里写作 Rs,同时也提到 RG)决定“搬得有多快”。

材料明确给出操作方向:可降低驱动电路内阻 Rs,减小时间常数,加快开关速度。

这句话背后就是经典的RC逻辑:

充电/放电路径电阻越大,电流越小;

电流越小,单位时间搬运的电荷越少;

栅压爬升或下降就越慢;

td(on)、tr、td(off)、tf 这些开关时间参数就被拉长。

而且材料对关断过程描述得很具体:关断延迟时间 td(off) 是 Up 下降到零开始,Cin 通过 Rs 和 RG 放电,UGS 按指数曲线下降到某个栅压点后,ID 才开始减小直至为零。

注意这里的关键点:UGS“按指数曲线下降”。

指数曲线意味着什么?意味着电阻稍微大一点,后面那段“尾巴”会非常拖,关断就容易出现你不想看到的慢吞吞。

“相互作用”到底是什么:Cin 不变时,Rs 才是你能拧的旋钮

把上面两段合起来,所谓“栅源电容与驱动内阻的相互作用”,本质就是:

开关速度由 Cin 的充放电决定,而 Cin 的充放电快慢由驱动内阻 Rs(以及相关栅电阻 RG)决定。

Cin 是客观存在的“货物量”,Rs 是“道路宽窄”。货多、路窄,就堵;货少、路宽,就顺。

材料也直接给出限制与空间:

Cin:使用者无法降低(基本受器件决定)

Rs:使用者可以降低(通过驱动设计优化)

所以在工程上你经常看到一种很现实的结论:同一颗MOS管,在不同驱动电阻、不同驱动芯片、不同走线和布局下,开关速度可能完全不是一个水平。

把开通过程拆开看,你会更理解“为什么看起来慢”

材料把开通过程分得很细:

开通延迟时间 td(on):Up 前沿到 UGS=UT 并开始出现 ID 的时间

上升时间 tr:UGS 从 UT 上升到进入非饱和区的栅压 UGSP 的时间

开通时间 ton:td(on)+tr

这三段其实对应三件事:

1)先把栅压推到阈值 UT,电流才“开始出现”;

2)继续把栅压推到某个与稳态电流相关的 UGSP,器件状态才真正切换到你想要的导通区间;

3)整个过程的长短,取决于栅极电压被推进去的速度——也就是 Cin 通过驱动电阻充电的速度。

因此当你看到“开通延迟变长、上升沿变缓”,第一反应不该是怀疑MOS“天生慢”,而是应该回头看:你的驱动内阻是不是把Cin的充电过程拖慢了。

为什么CMOS电路往往看起来更“利落”

材料里还有一句对比非常有用:MOS管的充、放电时间较长,会使MOS管的开关速度比晶体三极管低;不过在CMOS电路中,由于充电电路和放电电路都是低阻电路,因此充、放电过程都比较快,从而使CMOS电路有较高的开关速度。

这句话放到今天依然很“实用主义”:

低阻的充放电路径,会显著缩短时间常数;时间常数缩短,边沿就更干净,开关更快。

它再次强调了同一个核心:决定速度的不是你“给了一个逻辑高/低”,而是你能不能用足够低的等效电阻,把电容里的电荷快速搬完。

写在最后:别只盯MOS管参数,先盯“RC”

如果你此刻正在排查某个开关波形不利落的问题,最值得先记住的只有一句话:

MOSFET 的开关速度和 Cin 充放电关系极大;Cin 难以改变,但可以通过降低驱动电路内阻 Rs 来减小时间常数、加快开关速度。

你可以把它当作一个排查顺序:

先承认电容一定存在,再去优化它的充放电通道——这往往比反复更换器件更快接近答案。

你在实际电路里更常遇到“开通慢”还是“关断慢”?你可以把你的现象描述一下(比如哪一段边沿更拖、负载大概是什么),我们再沿着材料里的 td(on)、tr、td(off)、tf 的定义,把问题定位得更具体。

上一篇:mos管控制正极还是负极

下一篇:没有了

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN