发布时间:2026-02-03编辑:国产MOS管厂家浏览:0次

电容性负载在瞬态上电时往往会释放巨大的浪涌电流,让人防不胜防:一旦失控,不仅可能炸毁开关器件,还会对后级电路造成不可逆损伤。本文结合多年的项目经验,从低边开关思路切入,分享两种基于N-mosfet的浪涌抑制方案(E/F),并详解分压电阻的工程选型,助你在高低压系统中快速部署可靠的缓启电路。

回顾传统高边方案

曾有人只用单颗P-mosFET(方案A/C)做高边软启,它的电路简单,但当VIN上电、Q2/Q4尚未导通时,输出电容C9/C10/C19/C20只能绕经体二极管充电,并未彻底抑制浪涌。即使选型偏大RDS(on)余量,也只能降低而非消除瞬态冲击。

低边开关的优势

在成熟的同步BUCK设计中,低边开关通常选用N-MOSFET:

RDS(on)更低,导通损耗小;

栅极驱动仅需地电位及控制信号,无须高压驱动源;

接地侧插入,易于电流检测与系统隔离。

方案E:VCC ≤ VGS的低压实践

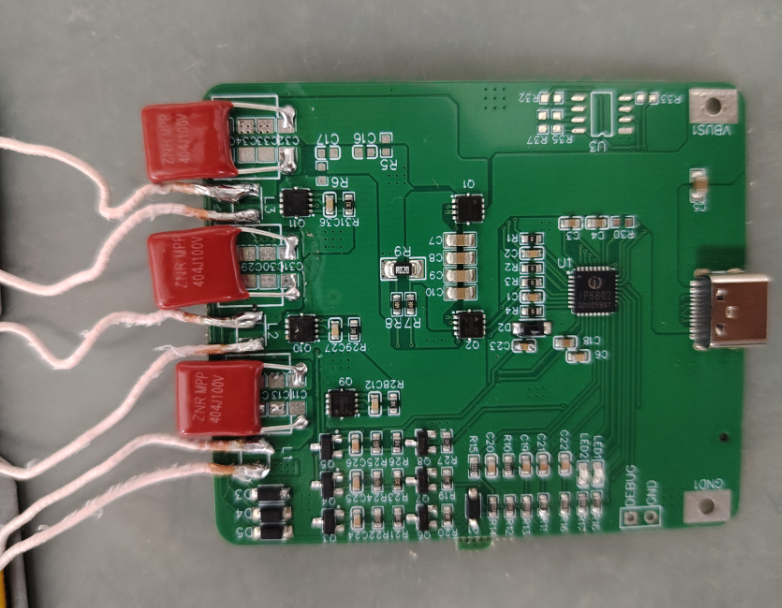

如图5.83所示,E方案将Q4置于地线侧,上电时通过栅极电阻R5(典型470 kΩ)限流,使输出电容沿着Q4的缓慢通道充电。当VCC不超过Q4的VGS(max)±20 V,完全无需额外分压,器件即可正常工作。

方案F:高压场景下的分压电阻计算

当系统VCC达到60 V或更高,就要在Q4栅-源间并联分压网络。以R5=470 kΩ、R6=47 kΩ为例:

VGS = VCC × 47 k/(470 k+47 k)

当VCC=60 V时,VGS≈5.45 V;

当VCC=100 V时,VGS≈9.09 V;

均远低于±20 V耐压,设计安全无虞。

体二极管电流路径对比

在高边方案B/D,上电时输出电容必须经P-MOSFET体二极管充电;低边E/F中,Q4的体二极管则保持反向偏置,输出电容仅从地线侧缓慢升压,瞬态大电流被从源头切断。

工程实现要点

• 栅极电阻R5:既要抑制dV/dt,也不能过大导致缓启过慢;

• 分压阻值:可按VGS(max)和允许误差留出10%裕量;

• PCB走线:地平面侧需优化接地回路,降低环路电感;

• 热耗评估:米勒平台期间RDS增大,会导致热损耗上升,必要时加装散热片。

典型应用场景

• 高边开关:电池反接保护、热插拔电源管理;

• 低边开关:地线侧电流检测、睡眠状态断电隔离、采集模块接地隔离。

多年的设计经验告诉我,选择低边N-MOSFET并配以合理分压电阻,是兼顾成本与可靠性的高效方案。欢迎在评论区分享你的实践心得或疑问,我们一同探讨更优解。

上一篇:集成电路与mos管的关系

下一篇:没有了

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN