发布时间:2026-05-05编辑:国产MOS管厂家浏览:0次

你以为“电源切换”只是把两路电接上、再用个开关选一路?真做过的人都知道:切得不干净,会互相“打架”;切得不够快,设备就会掉电重启;切得不够省,静态功耗又悄悄把电池耗空。

所以,双电源自动切换电路看似是小模块,实际上是系统稳定性的底座。今天就围绕两套典型思路——“单 Pmos + 二极管”与“三 MOS 管近似 0 压降方案”——把它们的工作机理、效率取舍、以及容易踩的坑讲清楚。

先把问题说透:双电源切换到底在解决什么?

最常见的场景是两路来源:

外部电源(比如 USB 5V)

电池(比如锂电池 VBAT)

设计目标也很明确:

外部电源在:优先用外部电源,同时让电池供电关断

外部电源断:立刻由电池顶上,尽量“无缝”

两路电不要互相倒灌,更不能把其中一路当成“被充电对象”或“被放电对象”

而 MOS 管之所以被大量使用,是因为它能当“开关”,并且导通电阻 RDS(on) 低,理论上可以把损耗压得很小。但 MOS 管也有一个绕不开的现实:寄生反并二极管。

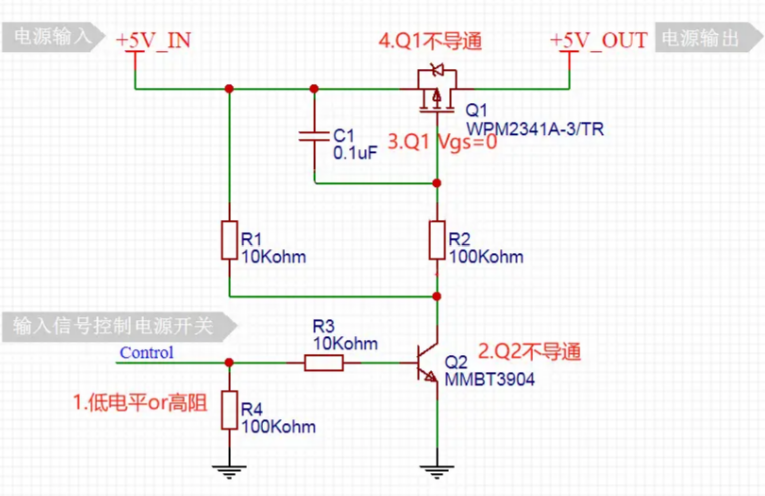

一、方案一:单 PMOS + 二极管,简单但有压降

第一套电路的结构非常直观:

VUSB:外部 USB 供电(5V)

VBAT:锂电池供电

Q1:PMOS

D1:二极管

VCC:负载电源端

它的核心逻辑是“外电在时,电池断;外电没了,电池接上”。

1)当 VUSB=5V 外部供电存在时

这时 PMOS(Q1)的 G 端电压为 5V。根据 PMOS 的导通特性,栅极电压高,Q1 不导通。于是电压通过二极管 D1 直接到达 VCC,负载由 USB 供电。

这一步的优点是:结构简单,切换逻辑清晰,基本不需要复杂驱动。

但缺点也很硬:二极管有压降。材料里提到最小约 0.3V——这对很多 3.3V 系统来说,可能意味着边界更紧、余量更少、发热和效率更差。

2)当 VUSB 断开后

VUSB 一断,原本 5V 的栅极电压会被电阻 R1 下拉到 GND。此时 Q1 的 S 端电压高于 G 端,满足 PMOS 导通条件,Q1 导通,VCC 由 VBAT 供电。

材料里还有一句很关键的话:在 MOS 管还未导通之前,S 端电压比 G 端高,因此 MOS 管会导通;导通以后,MOS 管的寄生二极管会短路,不再起作用。

这句话本质上在提醒你:MOS 管的寄生结构始终存在,但当 MOS 管进入正常导通状态后,电流走的是“低电阻通道”,寄生二极管不再主导压降与损耗。

所以,方案一是“能用、好用、容易用”,但它很难做到“几乎无压降”。

二、为什么很多人一提 MOS 切换就皱眉:寄生反并二极管的麻烦

材料里有一个非常现实的观点:用 MOS 管切换并不好设计,甚至不如继电器或接触器。原因就卡在寄生反并二极管上——你关断了 MOS,电流仍可能通过反并二极管走出一条“旁路”。

最典型的不合理现象是倒灌:

比如你用 MOS 切断电池供电,直流电源输出到负载。如果直流电源输出电压高于电池,就可能通过 MOS 管的反并二极管向电池“充电”。

注意,这里的问题不是“充电好不好”,而是“你根本没打算让它充”。没有受控的充电管理、没有限流与保护,这种路径很危险,也会引发系统行为混乱:电源优先级失真、发热、甚至损坏。

所以,只要用 MOS 做电源切换,你必须把“寄生二极管的方向”和“可能的倒灌路径”当作第一优先级去审视,而不是画完原理图才后知后觉。

三、方案二:三 MOS 管实现近似 0 压降,效率上去了,细节也更挑剔

如果你嫌二极管压降太大,第二套方案给了一条更“硬核”的路:利用 MOS 管低 RDS(on) 的特性,追求几乎 0 压降的主副电源自动切换。

电路由 3 个 MOS 管构成,主要电源为 VIN1(主电源),备用为 VIN2(外部电源),输出为 VOUT。材料以 3.3V 举例。

1)当 VIN1(主电源)为 3.3V 时

Q1 的 NMOS 导通

Q1 拉低 Q3(PMOS)的栅极,Q3 开始导通

此时 Q2 的 G-S 电压等于 Q3 PMOS 的导通压降,大概几十 mV

因为只有几十 mV,Q2 MOS 管关闭,VIN2 被断开

VOUT 由 VIN1 供电,且 VOUT=3.3V

这一段非常关键,它解释了“零压降”追求的底层逻辑:不靠二极管硬拦,而是利用 MOS 的低导通电阻来把损耗压到“几十 mV 量级”,从系统角度看接近 0 压降。

同时材料给出了静态功耗:I1 + I2 = 20uA。

这组数字意味着:当主电源在线、并且电路处于这种工作状态时,会有一个可计量的静态消耗。20uA 不算大,但在超低功耗设备里,它是需要被看见的。

2)当 VIN1(主电源)断开时

Q1 NMOS 截止

Q2 PMOS 的栅极通过 R1 下拉,Q2 导通

Q3 PMOS 的栅极通过 R2 上拉,Q3 截止

此时 Q1、Q3 截止,VOUT 由 VIN2 供电,为 3.3V

更有意思的是:当电路由 VIN2 供电时,静态功耗“消失了”,直接为 0

这就是方案二“看起来很美”的地方:不仅压降几乎没有,而且在外部电源供电时静态功耗为 0。材料也因此给出一个明确判断:在这个电路中,外部电源供电是更好的选择。

但是,别急着抄电路。材料同时给了两个非常实际的警告。

四、三 MOS 管方案的两个关键前提:器件指标与主电源下降隐患

前提一:三个 MOS 管都要“低导通电阻 + 低压”特性

因为你追求的是“几十 mV 级别”的压降,那么任何一颗 MOS 管的 RDS(on) 偏大、阈值特性不合适,都会让“近似 0 压降”变成“看图很美,落地很痛”。

前提二:主电源下降过程中可能出现异常通路

材料提到一个网友反馈的隐患:当主电源下降过程中,可能出现 Q3 未完全关断而 Q2 就开始导通,外电源通过 Q2、Q3 形成通路,阻止了主电源的降低。

翻译成工程语言就是:切换不是一个理想的瞬间动作,而是一段“过渡过程”。如果过渡窗口里两个开关状态重叠,就可能产生你最不想要的结果——两路电源被短暂连在一起,互相影响。

更麻烦的是,它不一定表现为立刻烧毁。它可能表现为:

主电源掉电曲线异常(降不下去)

切换时序变慢或不确定

系统某些电压域出现“拖拽”与回灌

某些场景下偶发复位、偶发异常

这也是为什么:越接近“无缝”和“零压降”,电路越像在走钢丝。你省掉的那 0.3V,往往是用更苛刻的器件选择与更敏感的时序条件换来的。

五、怎么选:简单可靠,还是极致效率?

把两套方案放在一起,你会发现它们不是谁“先进”谁“落后”,而是面对不同工程目标的两种取舍。

如果你的系统更在乎:

结构简单、可控、易调试

对压降不那么敏感

更希望行为确定、不在边缘状态“抖动”

那“单 PMOS + 二极管”会更踏实。

但如果你的系统更在乎:

尽量接近 0 压降

希望效率更高、发热更低

还希望在特定供电状态下静态功耗更优(材料里 VIN2 供电时为 0)

那三 MOS 管方案值得考虑,只是你必须接受:它对 MOS 管参数更挑剔,也必须正视主电源下降过程的潜在问题。

电源切换电路,表面是“供电路径”,本质是“系统边界条件管理”。你每一次想省掉的压降、每一次想做成的无缝,最后都会以另一种形式回到你面前:器件选型、时序窗口、倒灌路径、以及那些最难抓的偶发问题。

你更偏向哪一种设计目标:简单可靠,还是近似 0 压降的效率极致?你做过的项目里,最难搞的是压降、倒灌,还是切换瞬间的异常?欢迎把你的电路场景和供电参数放在评论区,我们可以把“看起来对”的方案,进一步推到“用起来稳”。

上一篇:mos管下拉电阻的取值

下一篇:没有了

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN