诺芯盛为您提供功率器件,高压MOS管、第三代半导体GaN、SiC等信息,敬请关注!

QQ:88650341(林生)

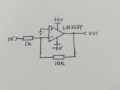

下拉电阻与电容协同选型是MOS管驱动电路的关键,需要考虑噪声滤波需求、开关速度平衡和dv/dt耐受能力。下拉电阻阻值的选择应结合电容参数进行优化。

文章总结:电容是电子工程中的关键元件,其性能受到栅极面积、氧化层厚度、材料介电常数和栅压变化等因素的影响。栅极面积越大,电容值越高,但增加开关速度可能降低。氧化层越薄,电容值越大,但可能导致漏电或击穿

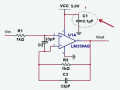

在MOS管栅极和漏极之间并联电容的设计考量主要关注抑制高频振荡和降低电压变化率,以平滑波形和降低噪声。然而,这种做法会显著增加等效的栅漏电容,加剧米勒效应。同时,过多并联电容可能导致开关损耗增加,甚至

本文深入探讨了MOS管开关速度中米勒电容效应的形成机制及其在电路设计中的关键影响。该效应核心源于MOS管内部存在的栅漏电容Cgd,通过效应放大机制影响开关特性瓶颈。当Vgs > Vth且Vds较高时,

MOS管栅极与漏极间加电容优化电路性能,提升信号稳定性、开关效率及EMI抑制,实现动态平衡。

MOS管输出电容影响电压变化,通过充放电机制影响开关性能,同时受米勒效应和静态漂移影响。

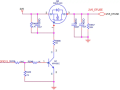

并联电容提升可靠性与效率,实现软开关,抑制电压尖峰,优化动态性能。

MOSFET DS并联电阻和电容可抑制开关浪涌、稳定工作及降低EMI。

文章探讨了栅极并联电容在米勒平台中的关键作用,优化其可有效降低开关损耗并抑制振荡,提升系统效率与可靠性。

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN