发布时间:2026-01-23编辑:国产MOS管厂家浏览:0次

当你调试一个推挽功率电路,满心期待看到平滑的输出波形时,示波器屏幕上却跳出一个刺眼的电压尖峰——这恐怕是许多硬件工程师都曾遭遇的“惊魂一刻”。这个看似微小的过冲,轻则引入噪声干扰系统性能,重则直接导致MOS管栅极氧化层击穿,让整个项目功亏一篑。在诸多成因中,寄生电容效应往往是最隐蔽、也最容易被低估的“元凶”之一。今天,我们就深入mos管的内部,拆解寄生电容如何发起“隐形攻击”,并探讨行之有效的实战抑制策略。

理解尖峰:从MOS管内部的“隐形电容”说起

要抑制尖峰,首先要理解它的诞生地。mos管并非理想开关,其内部物理结构天然形成了多个寄生电容,其中最关键的是栅源寄生电容(Cgs)和漏源寄生电容(Cds)。它们就像隐藏在开关路径上的“小水塘”,在高速切换的瞬间,决定了电荷流动的秩序或混乱。

当MOS管从开启状态切换到关闭状态时,驱动电路需要抽走栅极电荷。如果驱动能力不足或回路阻抗偏高,栅源寄生电容Cgs的放电过程就会变得迟缓。此时,栅极电压Vgs无法快速下降,导致MOS管未能及时进入完全关断状态。与此同时,主回路电流开始换向,电感能量寻求释放。这个延迟的关断过程与电感能量的释放时机重叠,一部分本应通过负载或吸收回路耗散的能量,便会耦合到仍处于半导通状态的MOS管通道上,在漏极电压Vds上形成一个显著的电压尖峰。

另一个“共犯”是漏源寄生电容Cds。在关断瞬间,急剧减小的漏源电流会使Cds迅速放电。这个放电电流流经电路中的寄生电感(如引线电感Ls)时,根据公式V = L * di/dt,会产生一个反向电动势。这个反峰电压直接叠加在MOS管的漏-源两端,进一步抬高了尖峰的幅值。可以这样理解:Cds和线路寄生电感在开关瞬间构成了一个谐振回路,其瞬态振荡直接表现为Vds上的振铃和过冲。

核心矛盾:开关速度与电压应力的权衡

这里浮现出一个经典的设计矛盾:为了提高效率、降低开关损耗,我们总希望MOS管的开关速度越快越好。然而,过快的开关速度意味着极高的di/dt和dv/dt,这会加剧寄生电容充放电电流的突变,从而激发更强烈的电感反峰和电压振荡。本质上,尖峰电压是电路寄生效应对高速开关动作的“反抗”。

因此,抑制尖峰的核心思路,并非一味追求极速开关,而是在开关速度、电压应力与电磁干扰之间取得精妙的平衡。这需要从器件选型、电路布局和拓扑优化三个维度协同入手。

抑制策略一:器件与布局的精细化设计

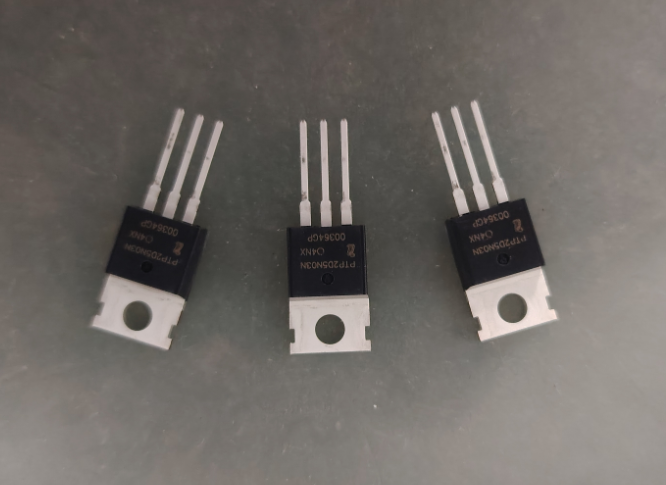

MOS管选型:关注器件的寄生电容参数。在满足电压电流定额的前提下,优先选择Coss(输出电容,包含Cds)和Ciss(输入电容,主要成分为Cgs)更小的型号。更小的寄生电容意味着充放电所需电荷量更少,在相同驱动条件下开关更快,且产生的充放电电流脉冲更小,从而从源头上减弱了激发电压尖峰的能量。

驱动电路优化:驱动电路必须提供足够强劲的“推力”和“拉力”。确保驱动芯片或电路能提供足够大的瞬间电流,以快速完成对Cgs的充放电,实现栅极电压的陡峭上升与下降,减少开关过渡时间。同时,驱动回路路径必须尽可能短而粗,严格最小化驱动回路的寄生电感,这是避免驱动信号振铃、保证开关控制精准的关键。

PCB布局的艺术:这是控制寄生参数最有效也最经济的环节。核心原则是减小高频大电流环路的面积。

功率回路:将输入滤波电容、上/下管mosfet、输出电感或负载的连接路径设计得尽可能短且宽,形成紧凑的环路,以最小化功率路径上的寄生电感(尤其是源极寄生电感Ls)。

驱动回路:驱动芯片的输出到MOS管栅极,再从MOS管源极返回驱动芯片地的路径,同样需要最短化。对于推挽电路中的高端管,采用自举电路供电时,自举二极管和电容应紧靠驱动IC和高端MOS管。

地平面设计:使用完整或至少是局部的接地平面,为高频噪声电流提供低阻抗回流路径,防止地线噪声耦合。

抑制策略二:吸收电路与软开关技术

当布局和驱动优化后仍有余波未平,吸收电路便成为直接“镇压”尖峰的最后一道防线。

RC吸收电路:在MOS管的漏极和源极之间并联一个RC串联网络,是最常见的尖峰吸收方法。其原理是利用电容C吸收尖峰电压的能量,再通过电阻R将这部分能量以热的形式消耗掉。参数选择至关重要:电容C值太小则吸收效果不足;太大则会增加开关开通时的容性损耗。电阻R值影响吸收速度和损耗,通常需要通过实验或仿真,在尖峰抑制效果与附加损耗之间取得折衷。

RCD钳位电路:对于电压尖峰特别高且能量较大的场合,可以采用RCD钳位电路。它通过一个快速二极管将尖峰电压的能量导向一个钳位电容,再由电阻释放,能更有效地将漏极电压钳位在一个安全水平。

软开关技术的进阶应用:对于追求极致效率和高频化的应用,软开关技术(如零电压开关ZVS、零电流开关ZCS)是治本之策。通过巧妙的谐振电路设计,使MOS管在开通或关断时,其两端电压或流经电流自然过零,从而从根本上消除了硬开关带来的电压电流重叠损耗和剧烈的电压电流变化率,寄生电容的充放电也变得平缓,尖峰电压自然得到极大抑制。尽管设计更为复杂,但在高端电源和电机驱动中已成为重要发展方向。

从分析到实践:一个思维框架

面对推挽电路中的尖峰电压问题,我们可以遵循以下步骤:

观测定位:使用带宽足够的示波器和近地探头,准确测量Vds和Vgs波形,确定尖峰的幅度、频率和出现相位。

成因分析:根据波形特征,判断尖峰主要来源于驱动不足(观察Vgs波形)、功率回路电感(分析电流路径),还是吸收不足。

针对性施策:针对分析结果,优先优化PCB布局和驱动,这是成本最低、效果最根本的方法。其次考虑调整吸收电路参数。在允许的条件下,评估更换更低寄生电容MOS管的可行性。

验证迭代:每次修改后重新测试,观察尖峰变化,直至将其控制在器件安全裕度和系统EMI要求之内。

电压尖峰的抑制,是电力电子工程师一场与寄生参数进行的微观较量。它没有一成不变的万能公式,更需要的是对器件物理特性的深刻理解、对电路布局细节的极致把控,以及在仿真与实验之间的反复求证。每一次成功地将那个刺眼的尖峰抹平,不仅是技术上的胜利,更是对电路内在规律的一次深刻对话。希望这份从原理到实战的“作战图”,能为你下一次与“尖峰”的对决提供清晰指引。

上一篇:mos管参数如何选择

下一篇:没有了

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN