发布时间:2026-01-29编辑:国产MOS管厂家浏览:0次

你是否还在为高边Pmos防反接电路的待机功耗和反灌风险而烦恼?在追求极致效率和可靠性的路上,工程师们早已将目光投向了一种更优解——高边NMOS配合专用驱动IC。这种设计虽增加了一丝复杂度,却换来了更低的导通损耗和更灵活的功耗控制,正成为破解特定设计难题的一把“利器”。

今天,我们就来深入拆解驱动IC+NMOS这一高边防反接方案,从原理内核到实战要点,一次讲清。

传统的防反接电路主要有三种:低边NMOS、高边PMOS以及高边NMOS+驱动IC。高边PMOS方案最为常见,结构简单,利用自驱效应导通。

但其存在两个固有短板:一是待机电流偏大,栅极下拉电阻会持续消耗电流;二是存在潜在的电流反灌风险。相比之下,NMOS具有更低的导通电阻(Rdson),意味着更小的导通压降和发热,效率更高。然而,挑战在于:要使高边NMOS完全导通,其栅极电压必须比源极(接电源正极)电压更高。这时,驱动IC的核心作用就是“无中生有”,从高边产生一个足够高的驱动电压。

目前主流方案依靠两种拓扑:

电荷泵型驱动IC:像一个“电压倍增器”,利用电容泵升电压。结构简单集成度高,但驱动电压可能存在纹波。

Buck-Boost型驱动IC:相当于一个小型开关电源,能稳定输出高于输入的电压,驱动能力更强,但电路相对复杂。

选型需权衡成本、板级面积、电压稳定性及待机功耗。

1. 栅极电阻(Rg)的精细考量

这个电阻至关重要:

抑制振荡:防止栅极回路寄生参数引发的高频振荡,避免栅极过冲击穿。

限流保平安:限制对栅极电容(Ciss)充电的峰值电流,保护驱动IC输出级。

控制开关速度:Rg值影响开通/关断速度,需要在开关损耗、EMI和可靠性间取得平衡,典型值在几欧姆到几十欧姆,需实验确定。

2. “沉默的守护者”:下拉电阻

在NMOS栅源极间并联一个大电阻(如10kΩ)必不可少。它在驱动信号无效时,为栅极提供确定的放电通路,确保MOS管可靠关断,是抗干扰的基石。

3. 待机功耗的终极对决

这是方案选型的核心权衡点。

PMOS方案:待机功耗主要来自栅极下拉电阻的分流。

NMOS+驱动IC方案:待机功耗主要来自驱动IC自身的工作电流。

对于长期深度待机设备,选用静态电流极低的驱动IC,整体待机功耗可能优于PMOS。对于持续工作的设备,PMOS方案可能效率更优。工程师必须根据产品实际工作占空比来精确评估。

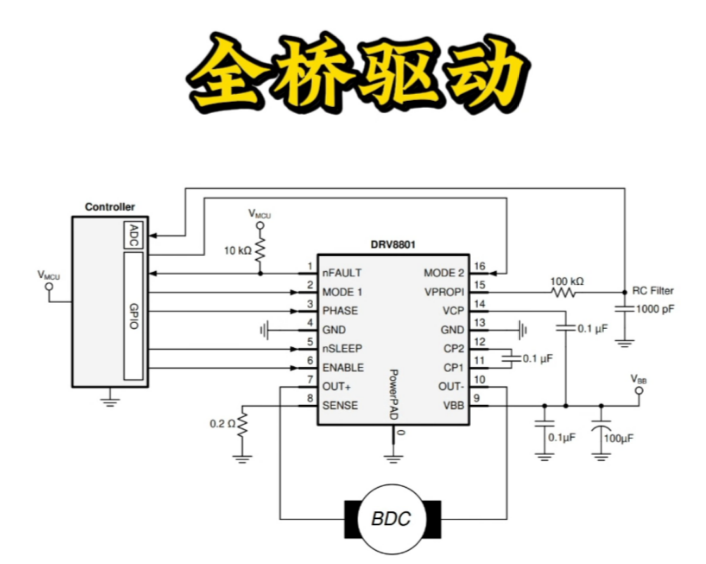

将视角扩展到半桥/全桥驱动,此方案价值更甚。此时,驱动IC不仅提供高边驱动,其输入侧的互锁逻辑功能至关重要。利用驱动IC的互补输入引脚(IN+/IN-)进行硬件互锁连接,可以从根本上防止上下桥臂直通,结合软件死区时间,构建双重保护。

布局上,驱动IC务必靠近其驱动的NMOS,以最短路径驱动,减小寄生电感。高边驱动的浮动地(源极)与主地之间的噪声隔离需通过紧凑布局和去耦电容妥善处理。

从防反接到多桥臂驱动,驱动IC+高边NMOS的方案体现了一种典型的工程思维:以局部设计的复杂度,换取系统整体性能的跃升。它打破了传统方案的局限,为工程师在效率、功耗与成本的三角博弈中提供了关键选项。

下次进行电源或电机驱动设计时,不妨将这一方案纳入你的评估清单。仔细算算功耗账与损耗账,或许它能帮你打开新的优化空间

上一篇:n沟道增强型mos场效应管

下一篇:没有了

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN